# Lecture Notes in Computer Science

4922

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Alfred Kobsa

University of California, Irvine, CA, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

*University of Dortmund, Germany*

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Manfred Broy Ingolf H. Krüger Michael Meisinger (Eds.)

# Model-Driven Development of Reliable Automotive Services

Second Automotive Software Workshop, ASWSD 2006 San Diego, CA, USA, March 15-17, 2006 Revised Selected Papers

#### Volume Editors

Manfred Broy

Technische Universität München, Institut für Informatik

Boltzmannstr. 3, 85748 Garching, Germany

E-mail: broy@in.tum.de

Ingolf H. Krüger

University of California, San Diego, Computer Science and Engineering

9500 Gilman Drive, La Jolla, CA 92093-0404, USA

E-mail: ikrueger@ucsd.edu

Michael Meisinger

University of California, San Diego

California Institute for Telecommunications and Information Technology

9500 Gilman Drive, La Jolla, CA 92093-0436, USA

E-mail: mmeisinger@ucsd.edu

Library of Congress Control Number: 2008930781

CR Subject Classification (1998): C.2.4, C.3, C.5.3, D.4, H.3-5, J.7

LNCS Sublibrary: SL 2 – Programming and Software Engineering

ISSN 0302-9743

ISBN-10 3-540-70929-0 Springer Berlin Heidelberg New York ISBN-13 978-3-540-70929-9 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2008 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12444144 06/3180 5 4 3 2 1 0

## Preface

Software development for the automotive domain has become the enabling technology for almost all safety-critical and comfort functions offered to the customer. Ninety percent of all innovations in automotive systems are directly or indirectly enabled by embedded software. The numbers of serious accidents have declined in recent years, despite constantly increasing traffic; this is correlated with the introduction of advanced, software-enabled functionality for driver assistance, such as electronic stability control. Software contributes significantly to the automotive value chain. By 2010 it is estimated that software will make up 40% of the value creation of automotive electrics/electronics.

However, with the large number of software-enabled functions, their interactions, and the corresponding networking and operating infrastructure, come significant complexities both during the automotive systems engineering process and at runtime. A central challenge for automotive systems development is the scattering of functionality across multiple subsystems, such as electronic control units (ECUs) and the associated networks. As an example, consider the central locking systems (CLS), whose functionality is spread out over up to 19 different ECUs in some luxury cars. Of course, this includes advanced functionality, such as seat positioning and radio tuning according to driver presets upon entry, as well as unlocking in case of a detected impact or accident. However, this example demonstrates that modern automotive systems bridge comfort- and safety-critical functionality. This induces particular demands on safety and security, and, in general, software and systems quality. The resulting challenges and opportunities were discussed, in depth, at the second Automotive Software Workshop San Diego (ASWSD) 2006, on whose results we report here.

Automotive systems are prime examples of the class of cyber-physical systems, i.e., systems that combine IT infrastructure and functionality with the control of physical processes. Consequently, the development process for automotive systems has to take into account both the physical environment and its representation in digital systems that get deployed in the vehicle. As an example, cars have a broad spectrum of timing requirements, ranging from hard real-time constraints at the level of motor control to soft real-time constraints at the level of infotainment systems. Automotive systems span the entire spectrum from time- and value-continuous, to mixed continuous and discrete, to discrete systems. The engineering processes used for automotive software have to take these and other domain-specific constraints into account – seamlessly from requirements elicitation to deployment and quality assurance.

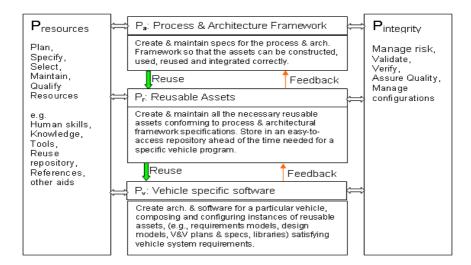

Increasingly, industry and academia try to address this challenge by introducing comprehensive requirements and architecture models that capture key domain aspects and enable exploitation in terms of code synthesis, simulation and, more generally, verification, and validation. A further goal in adopting a

model-based approach to automotive systems engineering is seen in the opportunity to decouple the *logical* from the *deployment* architecture of the vehicle. This decoupling holds the promise for a true product-line approach where conceptualizations of automotive systems structure and behavior are systematically reused across different car models. For instance, CLSs exist in almost all modern cars. Yet, we know that most software functions are developed afresh in the transition from one car model to the next. Furthermore, automotive manufacturers and suppliers hope to have models that help them contain the enormous space of variants and configurations that emerges from the possible combinations of software-enabled functions and their parameterizations.

Of course, due to the traditionally distributed engineering processes between OEMs (original equipment manufacturers, such as car makers) and multiple tiers of suppliers, models are needed that increase the precision and understanding in the communication between OEMs and suppliers. Consequently, to be of value, the models chosen need to be unambiguous to the highest degree possible, yet allow a broad spectrum of properties of structure and behavior to be specified. It is this tradeoff between precision and expressiveness that is a recurring theme through many of the contributions contained in this post-proceedings volume of ASWSD 2006.

Advanced development methods such as tailored development processes, structured systems and software architectures, model-driven development techniques and notations as well as formalized techniques of quality assurance have emerged as an approach to dealing with the mentioned demands and complexities, in particular during the analysis, specification and design phases of the development process. Such advanced development approaches have numerous benefits and advantages, including:

- They provide a basis for traceability from requirements specifications to implementation artifacts. This enables model-based requirements tracing, verification and validation approaches, and addresses systematic changes to models during the development process.

- They hold the promise of reduced turn-around times in iterative and incremental software and systems development. They enable engineers to explore model changes before changing the actual system.

- They support product-line software development by separating different functions for product line alternatives in an otherwise common, integrated model.

- Models, description techniques and associated development processes can be coordinated to provide contiguous, gap-free refinement and transformation steps from requirements to code. Models are connected and integrated to span all abstraction levels. This enables design tools, test and verification tools and code generators to work from the same sets of models to provide improved software quality.

On the infrastructure side, service-oriented architectures and automotive middleware platforms, such as AUTOSAR, are emerging as a means to manage the complex dependencies between vehicular functions, to provide standardized, scalable, and validated infrastructures.

Mastering the complexities of future-generation automotive software development poses a number of important, cross-disciplinary research challenges. The transition from monolithic to flexible, service-oriented solutions requires advances in all aspects of the development process; this includes, in particular, the selection of an adequate service model and corresponding development techniques, together with supporting software infrastructures.

The goal for ASWSD 2006 was to bring together experts from industry and academia who work on highly complex, distributed, reactive software systems related to the automotive domain, and to discuss and further the understanding of the following focus areas:

- Automotive models and model-driven development

- Automotive software and systems architectures

- Automotive domain architectures

- Automotive software services and service-oriented development

- Automotive hardware, middleware, and software platforms

- On- and off-board ad-hoc networking

- Networked automotive services

- Mobile sensor networks

- Reliability, security and privacy for automotive software

- Enabling technologies for telematics applications

The workshop took place March 15–17, 2006 in La Jolla, CA, USA, at the California Institute for Telecommunications and Information Technology (Calit2). It contributed to fostering a deeper understanding of the research challenges and agendas in this area. Potentials for cross-disciplinary research, as well as pertinent curricula and training programs to address these challenges, were identified and discussed.

The workshop program consisted of five keynote presentations, 13 technical paper presentations, a poster session and two panel discussions. The workshop spanned 2 1/2 days and was divided into the following topical sessions: Quality Assurance (QA), Real-Time Control (RT), Services and Components (SC), and Model-Based Development and Tools (MD). The pre-proceedings, consisting of the presentation slide sets, were made available at <a href="http://aswsd.ucsd.edu/2006">http://aswsd.ucsd.edu/2006</a>.

To foster discussion on cross-cutting and interdisciplinary topics, the organizers decided to have five keynote presentations – three from industry and two from academia, as well as two panel discussions as integral parts of the workshop program. Bruce Emaus (Vector CANtech), Rajesh Gupta (University of California, San Diego), Jeff Greenberg (Ford Motor Company), Thomas Kropf (Robert Bosch GmbH), and Alberto Sangiovanni-Vincentelli (University of California, Berkeley) were recruited as keynote speakers. Professors Frieder Seible (Dean, Jacobs School of Engineering, UCSD) and Larry Smarr (Director, Calit2) delivered opening remarks on the first day of the workshop.

The first keynote presentation, opening the Model-Based Development and Tools session, was given by *Bruce Emaus* (President of Vector CANtech). It was titled "Model-Based Development in the Upcoming Automotive Embedded Software Architecture of AUTOSAR." As automotive product architectures

continue to migrate toward higher levels of distribution with increasing system and software complexity, the use of model-driven automotive embedded software development is rapidly changing as the industry pushes forward with a new automotive software architecture called AUTOSAR. This presentation discussed both the essential business case for AUTOSAR and the design challenges of model-based software development in the automotive distributed embedded system domain.

Rajesh Gupta (University of California, San Diego) presented insight into new approaches for hardware design in his talk "Meta Modeling for Component Compositions: A Hardware Guy's View." He stated that novel computational fabrics are approaching intrinsic silicon efficiencies, imposing challenges to ensure programmability and program models. Currently, a methodology evolution occurs from chip design to embedded software design. The availability of programming models, methods and language support for building embedded systems (on chip) will be critical to exploiting the enormous technology capacities. New methods will mature that enable systematic modeling and exploitation of meta-data in design, verification, and synthesis. Gupta showed an approach to developing compositional, verifiable system-on-chip specifications in SystemC. He also hinted at opportunities for marrying service-oriented development techniques increasingly popular in software with a traditional system on chip development.

Jeff Greenberg (Manager of the VIRTTEX driving simulator at Ford Motor Company and Ford's Senior Technical Leader for automotive HMI) explained the challenge of automotive systems engineering from multiple angles. He focused on the necessity to create a simulation platform that not only is able to incorporate the emerging advanced software-enabled automotive systems, but also allows evaluation of the resulting human machine interface (HMI) concerns. The latter becomes increasingly important to ensure that the benefits of driver safety brought about by novel electronic features outweigh the increasing distraction drivers are exposed to (e.g., cell phone use during vehicle operation.)

Thomas Kropf (Vice President for system and software engineering, Driver Assistance Systems, Robert Bosch GmbH) delivered the keynote presentation "Driver Assistance Systems: Challenges for Automotive System and Software Design." He explained recent developments in the domain of driver assistance systems and described the challenges automotive suppliers are facing today in system and software design. He presented examples for new design methods, tools and processes which are used to overcome the current design limitations. Kropf's presentation pointed out the difficulty in applying traditional formal methods in the rich requirements spectrum of automotive systems outlined above.

Alberto Sangiovanni-Vincentelli (University of California, Berkeley) discussed the question "Is Embedded Software for Safety Critical Automotive Systems Really a Software Problem?" in his presentation, delivered by Manfred Broy. He stated that embedded software design is one, albeit critical, aspect of the more general problem of embedded system design, which is about the implementation of a set of functionalities satisfying a number of constraints ranging from

performance to cost, emissions, power consumption, and weight. Sangiovanni-Vincentelli's presentation illustrated the main challenges and opportunities of vertical design chain integration. In addition, it presented platform-based design as an important approach to meeting challenges and taking advantage of opportunities in automotive systems development. Platform-based design is a design methodology where reuse and programmability are central. It is an approach that provides unified and harmonious views on embedded software design and hardware architecture, consisting of formal techniques at the abstract level facilitating early verification with the correct set of tools and methods. The Metropolis environment was described as a framework to sustain the methodology.

Two panel discussions complemented the keynote presentations. The first panel discussed "Integrated Automotive System Development – Process, Challenges and Opportunities." Panelists were Jeff Greenberg (Ford Motor Company), Rajesh Gupta (University of California, San Diego), Edward Lee (University of California, Berkeley), and Wolfgang Pree (University of Salzburg). The panelists discussed the various phases of the automotive engineering process, into which the software/hardware co-design process is embedded. The malleability of software was discussed as a particular challenge in the seamlessness from early requirements to simulation to implementation and quality assurance. On the technical side, the panelists discussed the absence of adequate programming models that take time (hard- and soft real time) into consideration as a first-class citizen. Consequently, the spectrum from continuous to mixed continuous/discrete to discrete automotive software has yet to be mastered. The panelists formulated this as a challenge for the research community.

The second panel discussed "Model-Based Service Engineering for Automotive – Hype and Substance." Panelists were Bernhard Schätz (Technische Universität München, Germany), Bruce Emaus (Vector CANtech), Thomas Kropf (Robert Bosch GmbH), Klaus Müller-Glaser (University of Karlsruhe), and Daniel Gajski (University of California, Irvine). The discussion emphasized the increasingly distributed nature of functions realized by automotive software. Signals and information from components are combined in ways that were not intended originally. Service-oriented concepts can effectively help to manage the complexities caused by this heterogeneity. Initial approaches to introducing service-oriented concepts can already be found in industry – sometimes under different names. One of the biggest challenges is the absence of suitable models to describe the functions and their dependencies in a service-oriented way, in addition to existing implementation and hardware-oriented models of automotive controller components.

The discussion also emphasized the importance of approaching automotive system design from a user's view, focusing on the applications that the car as a system provides to its users. Automotive system services should be designed from the perspective of users and applications, not as a combination of pieces of functionality from existing components. The dependency of user-relevant services must be captured in suitable models.

Χ

In both panels, it was observed that in automotive system design the black-box controller business model, as a hardware/software unit of specification, integration, maintenance, and contract, is still predominant. This defines the OEM-supplier relationship. Providing pure software solutions to OEMs is currently not a viable business model for suppliers. Here, the industry needs to change and research needs to come up with suitable service-oriented business models and system development models. Automotive systems must open up to facilitate addition of new services – inside and outside of the vehicle. Infotainment systems were cited as likely first candidates to go in this direction.

A poster presentation session provided the opportunity to showcase current research projects for invited presenters from academia and automotive industry.

This volume includes a selection of refereed technical and invited papers presented at the workshop. In the following, we give a brief overview of the selected papers and their contents.

The paper "The Case for Modeling Security, Privacy, Usability, and Reliability (SPUR) in Automotive Software" by *Prasad et al.* emphasizes the importance of the attributes security, privacy, usability, and reliability (SPUR) in creating specifications for embedded in-vehicle automotive software. The paper reviews several real-world use-cases and their functional and non-functional system requirements. From there, the authors derive underlying automotive architectural elements spanning multiple software service domains. In particular, the suggested approach elevates the SPUR requirements from an afterthought to the earliest requirements and architecture design phases.

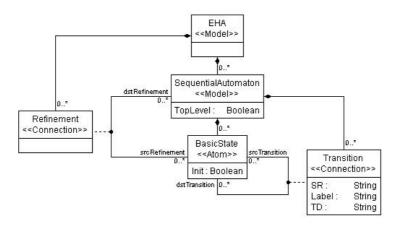

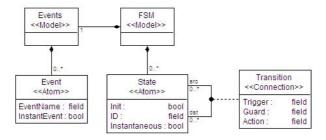

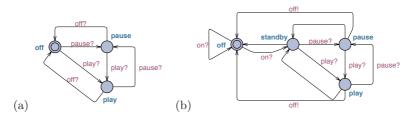

Neema et al. target the issue of model ambiguities across different tools and methods in their paper "Addressing Cross-Tool Semantic Ambiguities in Behavior Modeling for Vehicle Motion Control." They provide a model and semantics for behavior specifications in the automotive vehicle motion control (VMC) domain, facilitating the exchange of finite state machine models across different tools, and leading towards automated correct interpretation. The authors introduce an extended finite state machine metamodel (eFSM) with semantics definitions based on a mathematical framework. They show how models developed within commercial tool environments are checked for conformance with eFSM-models, promising higher-confidence software engineering for the VMC domain.

The paper "A Software and System Modeling Facility for Vehicle Environment Interactions" by *Nelson and Huang* describes an advanced modeling facility for system and software design, intended to address the growing complexity of automotive embedded software and the resulting issues for vehicle development. Increased complexity will require a broader range of modeling capabilities beyond functional/behavioral modeling. The authors present a more comprehensive modeling process with the capability to model vehicle systems from multiple viewpoints, such as the traditional functional point of view and the viewpoints of software structure, component interactions, and the human-machine interface. All viewpoints are brought together in a common set of models.

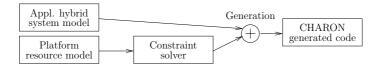

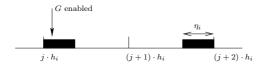

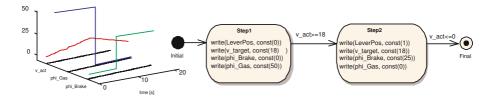

Anand et al. describe an approach for "Generating Sound and Resource-Aware Code From Hybrid Systems Models" in their contribution. The authors propose a framework for generating resource-aware code from hybrid systems models with guarantees of no switching discrepancies. They propose an approach to handling faulty transitions and compute execution rates for minimizing missed transitions. The approach is an effort at bridging the semantic gap between the model and the code due to discretization and resource constraints. This work helps to address remaining issues related to ensuring correctness of the implementation with respect to the model in model-based development of real-time embedded systems.

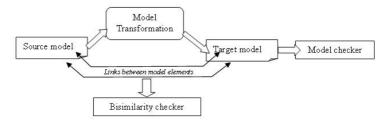

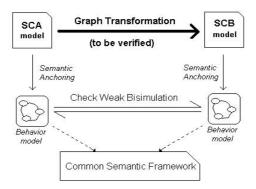

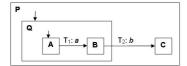

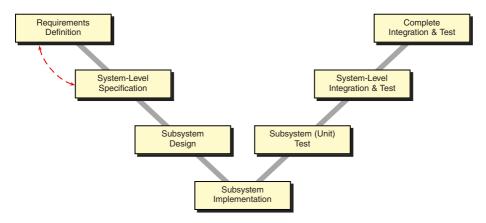

"Towards Verification of Model Transformations via Goal-Directed Certification," a contribution by *Karsai and Narayanan*, investigates a technique called 'goal-directed certification' that provides a pragmatic solution to the problem of verifying the correctness of model transformations within model-based development approaches. Model transformations include generating code from models, transforming design models into analysis models, and transforming a model between variants of a formalism (such as variants of Statecharts). The authors use concepts of bisimulation to verify whether a certain transformation instance preserved certain properties and subsequently extend this idea using weak bisimulation and semantic anchoring to a more general class of transformations.

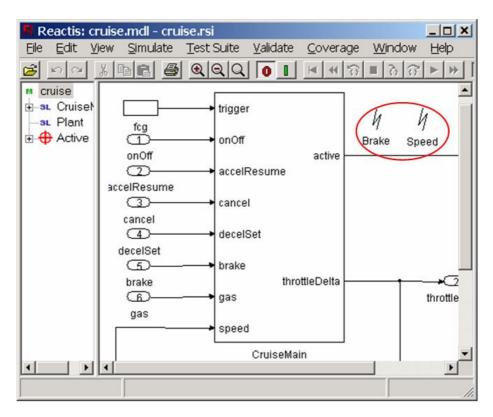

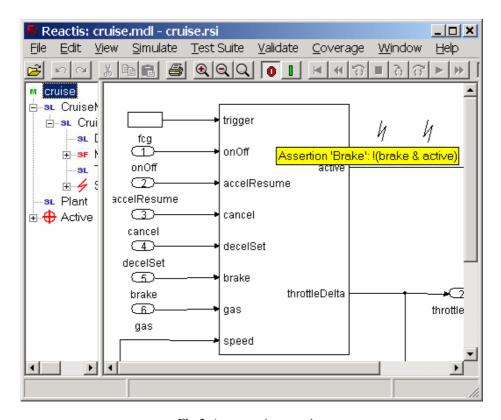

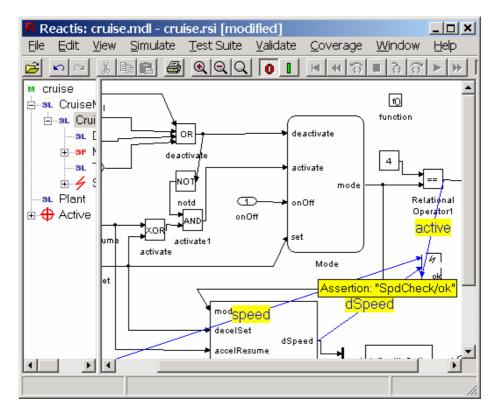

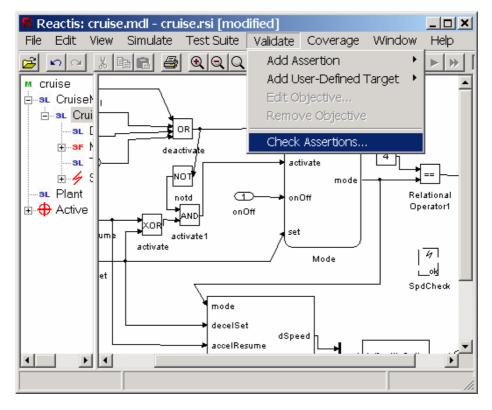

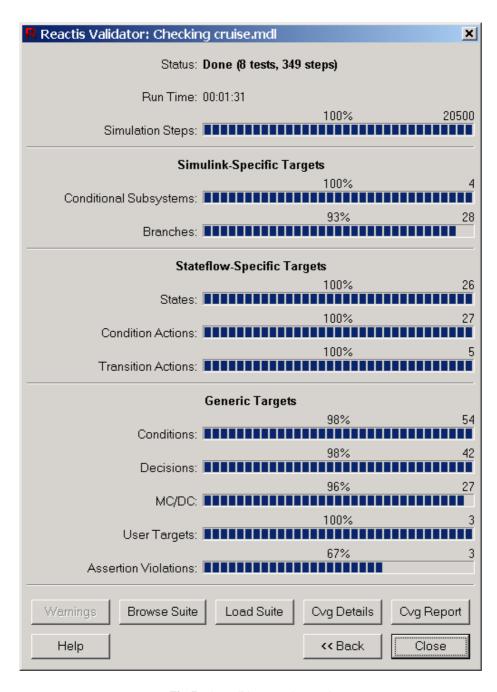

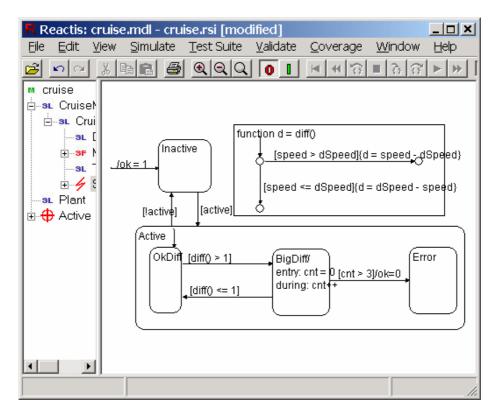

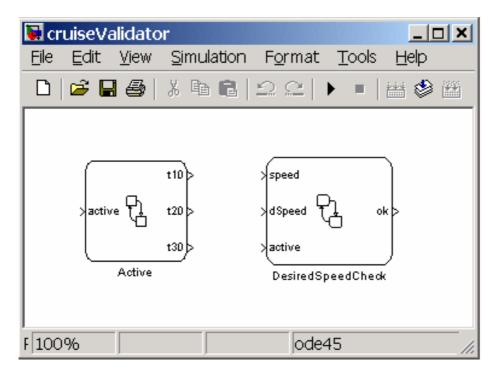

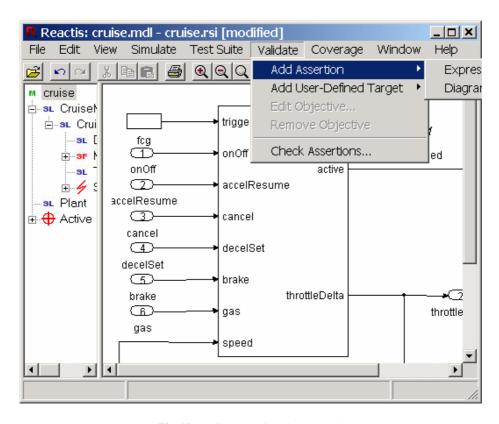

The paper "An Instrumentation-Based Approach to Controller Model Validation" by Cleaveland, Smolka and Sims discusses the concept of instrumentation-based validation (IBV): the use of model instrumentation and coverage-based testing to validate models of embedded control software. Assertions, formalized requirements, are realized through monitors that observe the behavior of executing controller models, which are instrumented with these assertions. The authors describe an implementation within the Reactis tool suite for the automated testing and validation of controller models given in Simulink/Stateflow.

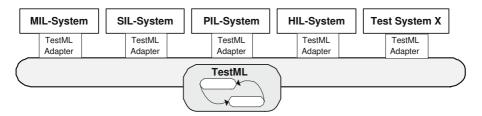

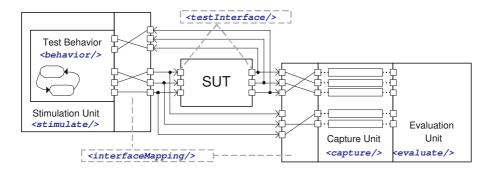

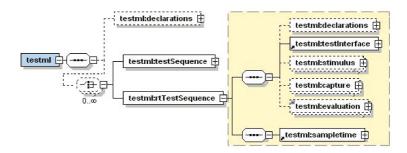

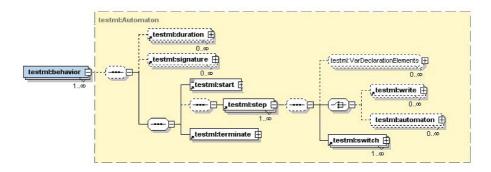

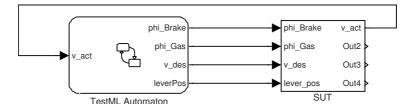

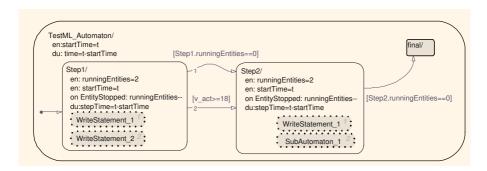

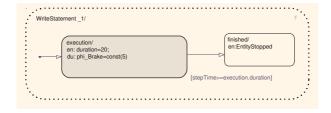

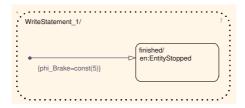

Grossmann et al. describe "TestML – A Test Exchange Language for Model-Based Testing of Embedded Software" in their contribution. TestML supports the exchange of tests between different test notations in a heterogeneous tool environment, for instance, facilitating the reuse of tests between different test levels, such as such as model-in-the-loop (MIL), software-in-the-loop (SIL), and hardware-in-the-loop (HIL) tests. The authors introduce the XML schema of TestML and demonstrate the efficiency of the interchange format by giving examples from the model-based development of electronic control units. Tool support is illustrated by an application with Simulink/Stateflow.

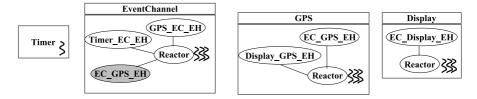

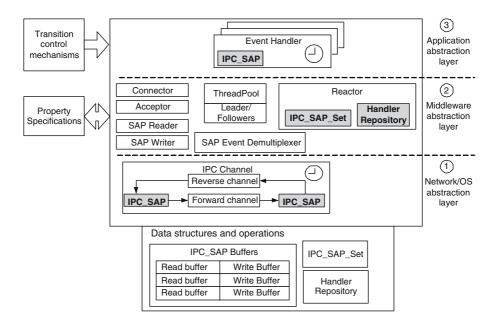

The paper "Towards Integrated Model-Driven Verification and Empirical Validation of Reusable Software Frameworks for Automotive Systems" by Subramonian and Gill claims that leveraging reusable software frameworks in the development of automotive systems offers significant potential to reduce engineering costs and cycle times, caused by rapidly increasing complexity and scale. The authors show the relevance of reusable software frameworks, describe an approach to verification and validation of such frameworks based on timed automata models, and present an evaluation of their approach.

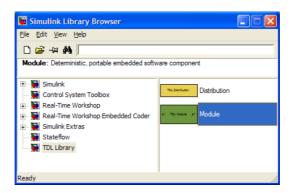

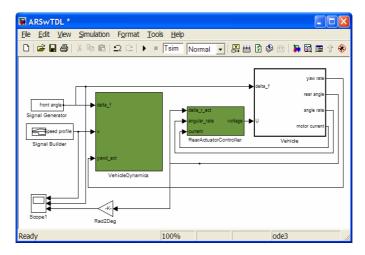

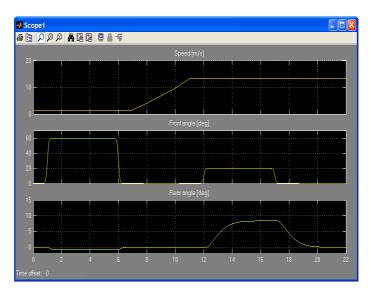

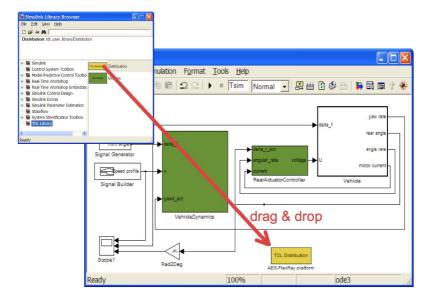

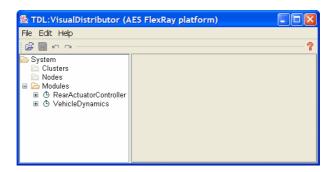

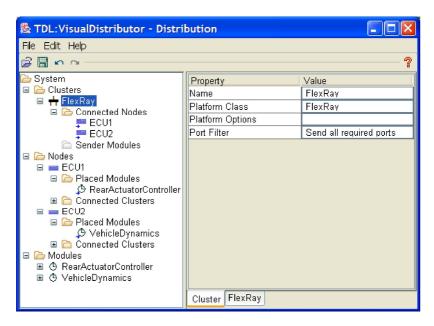

Pree and Templ describe in their paper "Modeling with the Timing Definition Language (TDL)" the model-based development process of hard real-time software with the TDL. They explain the modeling and simulation of TDL components in Matlab/Simulink, their mapping to a specific platform, and code generation. The authors claim that benefits of applying a TDL-based development process are significant development and maintenance cost savings, and, for instance, increased flexibility for automakers to change the execution platforms and, if necessary, redefine the OEM-supplier relationship.

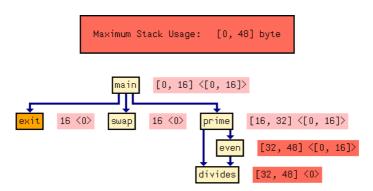

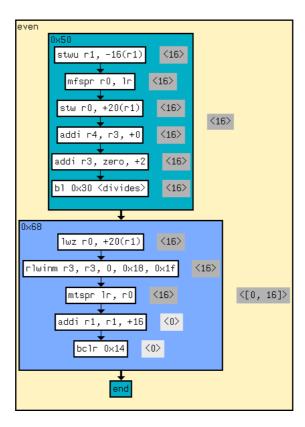

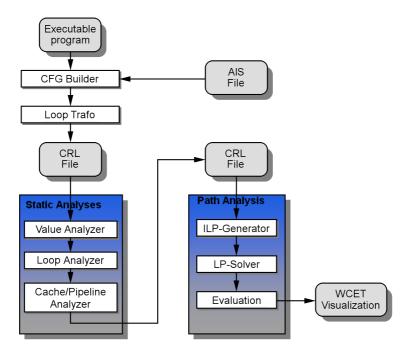

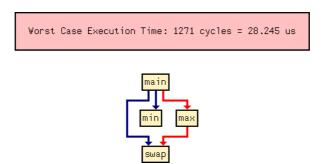

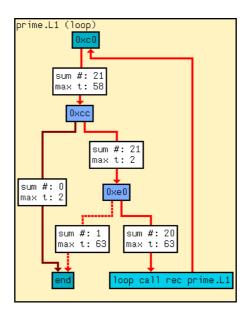

"Towards Model-Driven Development of Hard Real-Time Systems—Integrating ASCET-MD and aiT/StackAnalyzer" by Ferdinand et al. presents tools, experimental integration, preliminary results, and plans for further tool integration of automatic code generators such as ETAS' ASCET, and static program analysis tools like AbsInt's StackAnalyzer and the timing analyzer aiT. Through an integration of these tools it is, for instance, possible to give ASCET users a direct feedback on the effects of their design decisions on resource usage, allowing them to select more efficient designs and implementation methods, by making aiT/StackAnalyzer analysis results accessible from within ASCET.

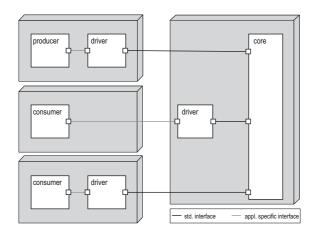

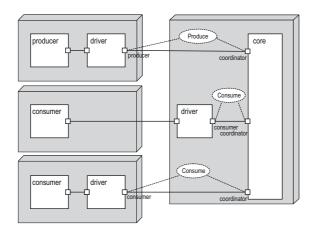

Finally, *Giese* introduces "Reusable Services and Semi-Automatic Service Composition for Automotive Software." The author describes a service-oriented approach for the reuse of automotive software functions across models; it exploits a recombination of functions in a restricted manner in order to enable reuse. The author shows how all phases of the development process can benefit from a service-oriented approach and describes how advanced synthesis techniques can be employed to reuse components, patterns, and services and compose them with only minimal manual efforts.

The workshop clearly exhibited the state of the art of model-based automotive software engineering and pointed out various challenges in the area. This is also reflected by the papers selected for this volume.

The organizers were delighted to again observe the extremely positive experience created through the dialog between leading researchers and industry participants from the USA and Europe. During the workshop significant progress was achieved to develop a common understanding of the challenging problems in the automotive domain such as:

- Models and model-transformations for hard and soft real-time systems

- Comprehensive engineering approaches for model-driven hardware/software co-design

- Integrating HMI design and development with automotive systems engineering processes

- Transitioning from component- to service-oriented systems engineering to support product-line development and reuse

The comments we received from participants during and after the workshop were overwhelmingly positive. In particular, the combination of and balance between industrial and academic participation with high-quality contributions from both sides was remarked as a distinguishing positive element of this workshop series.

The organizers and editors extend their profound thanks to all workshop participants, authors, keynote speakers, panelists, poster presenters, reviewers, sponsors, and members of the local organization team for their important contributions to the success of the workshop itself and of this post-proceedings volume.

This material is based on work supported by the National Science Foundation under Grants No. CNS-0413136 and CCF-0702791. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the National Science Foundation.

February 2008

Manfred Broy Ingolf H. Krüger Michael Meisinger

## **Organizers**

Manfred Broy Ingolf H. Krüger Michael Meisinger

#### Referees

Sushil Birla

Rance Cleaveland

Mirko Conrad

Werner Damm

Frederic Doucet

Claudiu Farcas

Christian Ferdinand

Christopher Gill

Carlo Ghezzi

Jürgen Grossmann

Stefan Henkler

Gabor Karsai

Hermann Kopetz

Edward Lee

Holger Giese

Thomas J. Giuli

Klaus Müller-Glaser

Sandeep Neema

Edward Nelson

K. Venkatesh Prasad

Wolfgang Pree

Stefan Resmerita

Alberto Sangiovanni-Vincentelli

Bernhard Schätz

Doug Schmidt

Joseph Sifakis

Gerald Stieglbauer

Janos Sztipanovits

Shigeharu Teshima

## Local Arrangements

Barbara Haynor Steve Hopper Alexandra Hubenko-Baker Michael Meisinger

## Thanks To

David Bareno Maureen C. Curran DeAndra Green Barbara Haynor David Hutches Jürgen Schulze

## **Sponsors**

California Institute for Telecommunication and Information Technology (Calit2) National Science Foundation (NSF)

## **Table of Contents**

| Modeling Techniques and Infrastructures                                                                                        |     |

|--------------------------------------------------------------------------------------------------------------------------------|-----|

| The Case for Modeling Security, Privacy, Usability and Reliability (SPUR) in Automotive Software                               | 1   |

| Addressing Cross-Tool Semantic Ambiguities in Behavior Modeling for Vehicle Motion Control                                     | 15  |

| A Software and System Modeling Facility for Vehicle Environment Interactions                                                   | 34  |

| Model Transformations                                                                                                          |     |

| Generating Sound and Resource-Aware Code from Hybrid Systems Models                                                            | 48  |

| Towards Verification of Model Transformations Via Goal-Directed Certification                                                  | 67  |

| Quality Assurance                                                                                                              |     |

| An Instrumentation-Based Approach to Controller Model Validation $\dots$ Rance Cleaveland, Scott A. Smolka, and Steven T. Sims | 84  |

| TestML - A Test Exchange Language for Model-Based Testing of Embedded Software                                                 | 98  |

| Towards Integrated Model-Driven Verification and Empirical Validation of Reusable Software Frameworks for Automotive Systems   | 118 |

| Real-Time Control                                                                                                              |     |

| Modeling with the Timing Definition Language (TDL)                                                                             | 133 |

## XVIII Table of Contents

| Towards Model-Driven Development of Hard Real-Time Systems: Integrating ASCET and aiT/StackAnalyzer | 145 |

|-----------------------------------------------------------------------------------------------------|-----|

| Services and Components                                                                             |     |

| Reusable Services and Semi-automatic Service Composition for Automotive Software                    | 161 |

| Author Index                                                                                        | 183 |

# The Case for Modeling Security, Privacy, Usability and Reliability (SPUR) in Automotive Software

K. Venkatesh Prasad, Thomas J. Giuli, and David Watson

Ford Motor Company, Dearborn, MI 48121, USA {kprasad,tgiuli,dwatso80}@ford.com

Abstract. During the past few years, there has been considerable growth in the practice of modeling automotive software requirements. Much of this growth has been centered on software requirements and its value in the context of specific functional areas of an automobile, such as powertrain, chassis, body, safety and infotainment systems. This paper makes a case for modeling four cross-functional attributes of software, namely security, privacy, usability, and reliability, or SPUR. These attributes are becoming increasingly important as automobiles become information conduits. We outline why these SPUR attributes are important in creating specifications for embedded in-vehicle automotive software.

Several real-world use-cases are reviewed to illustrate both consumer needs and system requirements — functional and non-functional system requirements. From these requirements the underlying architectural elements of automotive SPUR are also derived. Broadly speaking these elements span three software service domains: the off-board enterprise software domain, the nomadic (device or service) software domain and the embedded (in-vehicle) software domain, all of which need to work in tandem for the complete lifecycle management of automotive software.

#### 1 Introduction

The nature and terrain of computing in the automobile is in a state of transition. Automotive computing is transforming from being function-oriented to being service oriented, while the terrain (or logical boundaries) of computing in an automobile is expanding to include both computing elements in the wireless external infrastructure and the nomadic (or hand held, mobile) infrastructure. This transition is being driven on the one hand by consumers, wanting to keep pace with their changing life styles and, on the other hand, by regulatory agencies placing more stringent demands on the attributes such as safety, emissions, fuel economy. Given the transformation in the nature and terrain of automotive computing, this paper makes the case for modeling security, privacy, usability and reliability (SPUR) — motivated in part by David Patterson's manifesto [1].

For nearly a century, the automobile was defined by components with local functionality and differentiated by proprietary systems engineering implementations involving mostly mechanical coupling between components. Over the past three decades, with the advent of microelectronics and local-area networks [2] in the automobile, there has been a steady growth in the use of mechatronics [3] and the practice of allocating functions across multiple components. The applications of systems engineering principles, in turn has been extended to a combination of mechanical, electronic, digital, analog (or discrete-time, continuous-time) sub-systems and components. With the growing maturity of the software ecosystem [4], including operating systems, programming languages, development environments, and engineering tools, the modern automobile is being increasingly defined by software. There is a trend to allocate automobile functions across multiple standardized components (to reduce the number or unique hardware modules) and to use software design, modeling and engineering for function implementation and associated product differentiation [5]. In this context, the automobile is rapidly becoming a distributed computing environment.

Commensurate with the growth in demand for new features, from both consumers and regulatory agencies, is the increase in the complexity of functional allocation across the distributed computing environment in the vehicle. In addition, the computing terrain of the automobile is rapidly changing [6]. With the advent of wireless personal, local, and wide-area technologies, the physical boundary of the automobile is no longer the logical bounding box for functional allocation. Functions may be distributed across on-board computing units [5], off-board (such as roadside) infrastructure units [7] and nomadic devices [8] such as cellular phones.

To manage this growth in the complexity of allocating functions, a higher level of abstraction will likely be required. A service-oriented computing approach [9] is an attractive option. The present day automobile is function-defined — most consumer perceived features are based on the specification of distributed onboard functions; the future automobile will likely be service-defined, with features being specified, modeled and synthesized by aggregating consumer and vehicle related services from both on-board and off-board sources.

The next section (Section 2) of this paper elaborates the case for SPUR in the automotive context and outlines the role of modeling SPUR. Section 3 introduces two broad examples that highlight the new computational terrain of the automobile and the role of modeling SPUR in these contexts: one example shows how the computational terrain logically extends from the the physical boundaries of the automobile into the roadside infrastructure and the second example illustrates how the new automotive computational terrain extends through nomadic devices and services into the wide area communication networks (such as the wireless telephony networks and, in general, the wireless internet). Section 4 shows how SPUR attributes associated with a specific use-case could be modeled. Section 5 lists requirements for tools needed to develop SPUR models. Section 6 discusses related work. Section 7, in conclusion, summarizes the need to model SPUR in the automotive context.

### 2 SPUR in the Automotive Context

SPUR [1] was advocated on the premise of shifting research efforts in computer science and engineering away from making faster, cheaper systems to making systems that are more secure, privacy-preserving, usable, and reliable. While these attributes can take on many meanings, we are interested in applying them to the experience of the individual people who own and interact with these systems on a daily basis. For example, while security and reliability can be seen as two sides of the same coin from a technology perspective, from a user's perspective they are two very distinct concepts. A system that constantly fails impacts a user very differently from a system that causes her credit card to be stolen. In this context, we believe that the automotive industry is particularly well-suited to understand the value of each aspect of SPUR-oriented design.

Security in the automotive domain has so far emphasized physical security. The first automobiles were produced without any built-in theft deterrents. Gradually they acquired keys to start the engine and door locks to protect property left in the vehicle. Modern vehicles now use sophisticated radio transmission devices with strong cryptography to prevent unauthorized entry.

Network connectivity is being added to vehicles through telematics services (e.g., OnStar, ® BMW ASSIST<sup>TM</sup>) and hands-free telephony, introducing the possibility of remote intrusion into a vehicle's embedded networks. Not only could a remote intrusion compromise the physical security of the vehicle (i.e., unauthorized remote unlock), but it could directly affect the vehicle's drivability. For example, a virus could trigger the vehicle's theft alarm while driving. Clearly, as the automotive industry integrates more digital network technology into vehicles, its impact on both physical and digital security must be assessed.

On the flip-side of the security coin is a concern for privacy. Modern vehicles "know" much more about their drivers and passengers than ever before. Vehicular navigation systems could be used to correlate data and extract potentially private information. For example, correlating driver location data with the locations of points of interest such as stores, places of worship, community centers and other buildings an organization can build an accurate profile of the driver's interests. The privacy concerns of automobile customers must be treated seriously and safeguarded with the introduction of new technologies such as telematics and navigation services.

The usability aspect of SPUR in the automotive context is especially important because of its impact on safety. An automobile's human-machine interface (HMI) must allow the driver to focus on the task of driving while at the same time providing un-occluded access to driver information as well as comfort and convenience features such as climate and radio controls. Complicating the matter are the integration of new technologies such as mobile phone services, voicemail, messaging, and email into the vehicle HMI. A balance must be struck between the complexity of an HMI with many features and safe usability.

Reliability has been a serious concern in the automotive industry and in the consuming public's minds for some time now. Automobiles are increasingly becoming software-driven, not just mechanically driven. Therefore, software reliability will be as important as mechanical reliability in future automobiles.

Table 1 outlines automotive examples that exhibit varying combinations of SPUR attributes. Each row categorizes examples as having or lacking some SPUR attributes. In the text that follows, we describe the reasoning behind the values assigned for each row:

- The Carfax® web service allows anyone to view detailed maintenance and accident histories of any vehicle for a fee. The service must be secure to prevent unauthorized tampering with vehicle records, usable enough for anyone to understand, and reliable to provide correct information. It's important to note that we're considering these attributes from the perspective of an individual user of the system. In this context, these attributes are neither orthogonal or rigorously defined. Instead, these attributes are intended to direct attention to attributes that can be easily overlooked when designing systems that are bigger, better, and faster.

- Safety is the primary concern of anti-lock braking systems (ABS) and so naturally the desire for reliability is high. Along similar reasoning, ABS must be easy and intuitive enough in its function such that untrained drivers can use the system. Security is as much of a concern as for any safety-critical module and should not be vulnerable to remote attack. Privacy is not much of a concern because the ABS does not collect or process any sensitive data to function properly.

- Comparing a standard door key and a valet key, we see that they are similar except in the privacy attribute. Both keys and their associated locking mechanisms must be secure enough to prevent people without keys from entering, both must be highly usable and reliable. However, while a standard door key should grant the holder access to all parts of the vehicle, the valet key is designed to prevent the valet from entering "private" areas, such as gloveboxes or trunks.

**Table 1.** Examples illustrating SPUR in an automotive context and the relative importance (Low, Medium, High) of each SPUR attribute to each example

| Example                  | S            | Р         | U | R |

|--------------------------|--------------|-----------|---|---|

| Carfax® database         | Η            | L         | Η | Н |

| Anti-lock braking system | ${\rm M}$    | ${\bf L}$ | Η | Η |

| Door key                 | $_{\rm H}$   | ${\bf L}$ | Η | Η |

| Valet key                | $\mathbf{H}$ | Η         | Η | Η |

The examples shown in Table 1 have software that resides either wholly inside the vehicle, or entirely outside the vehicle. Conversely, software implementing sophisticated telematics services reside not only on-board the vehicle but also off-board, including the IT infrastructure of original equipment manufacturers (OEMs), dealerships, telecommunications operators, and in hand held consumer

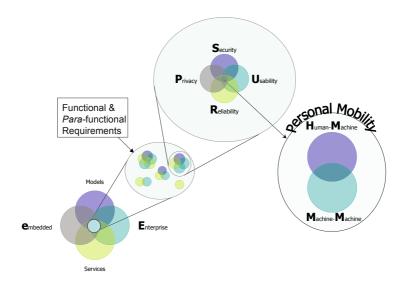

Fig. 1. Diagram of automotive SPUR

devices. Because of the new push of automotive software across module and vehicular boundaries, there is a need to develop models that cross these boundaries as well. Furthermore, because vehicular telematics software relies on dynamic external software, models of telematics systems must change along with deployed systems. A service-oriented approach to implementing automotive software — both in-vehicle software as well as enterprise software — eases the design, implementation and maintenance of systems to ensure that each requirement of SPUR design is present in the system.

Figure 1 illustrates this interesting space. As we stated before, we believe it is important to understand how to model services that cross the embedded and enterprise domains. Within this space are both functional and para-functional (or non-functional) requirements. Functional requirements are more visible, however we believe that the para-functional requirements will be increasingly important. In particular, we are interested in understanding how the mobility inherent in a vehicle impacts this space. Providing functionality to a person driving at highway speeds requires strong attention to SPUR both at the human to machine interface as well as the machine to machine interface. The safety and quality of the driving experience is clearly affected by these attributes. At the same time, designing computer communications systems that support SPUR concerns in these types of mobile applications requires careful attention to system interactions.

## 3 Examples of Automotive Services

In this section we use two examples to demonstrate the trend towards automotive services extending outside the physical constraints of the vehicle. The

first is the Vehicle Infrastructure Integration (VII) project [7]. The second is the Vehicle Consumer Services Interface (VCSI) project [8]. These two examples demonstrate integration of the vehicle with roadside infrastructure and consumer services respectively.

#### 3.1 VII

The Vehicle Infrastructure Integration project is a joint effort involving the United States Department of Transportation (USDOT), state transportation departments, and vehicle manufactures. The VII goal is to develop and deploy the roadside and vehicular infrastructure needed to improve the safety of the nation's roadways. By improving the amount and types of information available from the roadway and by having improved safety warnings and controls, drivers will be better prepared to mitigate or avoid accidents. The features enabled by VII include everything from warning drivers that another vehicle is about to run a red light, to notifying drivers that a given section of road is covered with ice.

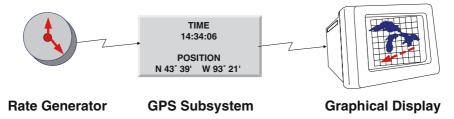

The VII roadway system consists of roadside units (RSUs) deployed along highways and onboard units (OBUs) built into vehicles that communicate with each other using the Dedicated Short Range Communications (DSRC) protocol at 5.9GHz. The roadside units are wired to an information services backend that can track traffic conditions as well as log safety problems throughout the system. Vehicles transmit useful sensor data, such as GPS location, velocity, and traction to the roadside units, which in turn process the sensor data and report back to vehicles in the area if any safety issues may be present. For example, if several vehicles report that their traction control and anti-lock brake systems were activated at the same spot on the highway, the roadside unit nearest the problem area can broadcast a warning to oncoming vehicles. Vehicles can also communicate with other vehicles directly, enabling dynamic warnings such as a vehicle notifying the vehicles directly behind it that the driver is braking suddenly.

Table 2 lists the titles assigned to some of the first scenarios being considered. In addition, it highlights how important the SPUR attributes are to each scenario. In general, scenarios that are likely to affect driver behavior or well-being have a high impact from security. For example, an incorrect signal that an emergency vehicle is approaching could cause great headaches to drivers, and potentially disrupt the usage of this signal by true emergency vehicles. Thus, it's important that such a system be secure against malicious manipulation. On the other hand, spurious information about traffic is less likely to significantly impact drivers, hence it is listed as having medium importance relative to security. Privacy is more of a concern when revealing information about specific vehicles, as in the case of intersection warnings. On the other hand, road conditions are likely to be broadcast to everybody, and therefore unlikely to contain a

<sup>&</sup>lt;sup>1</sup> It's important to note that we're talking about a subjective measure of security for illustrative purposes. We strongly believe that all of these attributes are important considerations for any scenario.

H L H H

HLHH

| Use case                                   | $\mathbf{S}$ | Р            | U         | ${\bf R}$ |

|--------------------------------------------|--------------|--------------|-----------|-----------|

| Emergency Brake Warning                    | Μ            | L            | Η         | Η         |

| Curve Speed Warning                        | Μ            | $_{\rm L}$   | Η         | Η         |

| Traffic Signal Violation Warning           | Η            | ${\rm M}$    | Η         | Η         |

| Stop Sign Violation Warning                | Η            | ${\rm M}$    | Η         | Η         |

| Emergency Vehicle Approaching              | Η            | $_{\rm L}$   | Η         | Η         |

| In-Vehicle Signage                         | Μ            | $\mathbf{L}$ | ${\rm M}$ | Μ         |

| Traffic Information and alt route guidance | Μ            | $\mathbf{L}$ | ${\rm M}$ | Η         |

| Electronic payments                        | Η            | $_{\rm H}$   | ${\rm M}$ | Η         |

| Roadway Condition Information              | Μ            | $_{\rm L}$   | Η         | Η         |

|                                            |              |              |           |           |

**Table 2.** List of VII use cases and the relative importance (Low, Medium, High) of each SPUR attribute to each use case

significant privacy risk. In general, usability and reliability are significant to all of these scenarios. In some cases, usability is less important, since the consequences are less severe.

Traffic Management

Emergency Vehicle At Scene

#### 3.2 VCSI

The second project, the Vehicle Consumer Services Interface (VCSI), is a project at Ford to provide an interface between consumers, their personal devices, off-board services, and vehicle systems including both networks and devices. VCSI is implemented as a service-oriented architecture, meaning that functions within the vehicle are designed as services to be used by other functions and may reside on one or more hardware modules. This design philosophy has advantages such as code reuse between modules and reduces the impact of the redesign of a module. For a more extensive treatment of VCSI see [8].

To demonstrate this system, we developed a prototype vehicle that contained several specific applications including those shown in Table 3. As with the VII examples above, we've made some attempt to demonstrate the relative importance of each SPUR attribute to each service. Since most of the consumer facing

**Table 3.** List of VCSI services and the relative importance (Low, Medium, High) of each SPUR attribute to each service

| Service                           | S | Р            | U         | R         |

|-----------------------------------|---|--------------|-----------|-----------|

| Vehicle Personalization           | L | Н            | Μ         | Η         |

| Personal Information Management   | Η | Н            | ${\rm M}$ | ${\rm M}$ |

| MyHome (Home Automation Services) | Η | Н            | ${\rm M}$ | ${\rm M}$ |

| Bluetooth Technology              | Η | Н            | ${\rm M}$ | ${\rm M}$ |

| Real-time navigation              | Μ | $\mathbf{L}$ | Μ         | Η         |

| Diagnostics                       | Η | Μ            | Η         | Η         |

| In-vehicle media player           | Μ | Μ            | Μ         | Μ         |

services provided by VCSI are not safety critical, they have lower requirements on usability and reliability. At the same time, most of these services depend on interfacing with devices that have personal information. In that context, it's important that the privacy of the data contained within those devices be kept secure.

Overall, we think these two projects demonstrate an increasing trend towards increased connectivity with a vehicle, both from consumer devices and from roadside infrastructure. In addition, we believe that modeling provides the means to understand these services provided to the consumer at a system level.

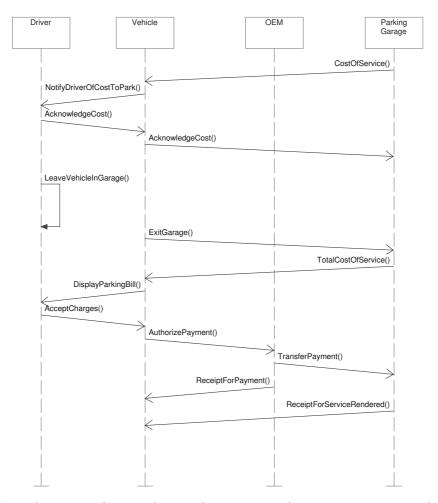

**Fig. 2.** A sequence diagram showing the interactions between entities in a parking garage with an electronic payment service. In this scenario a driver parks her car in a smart parking garage and electronically pays upon exit.

## 4 Electronic Payment Use Case

In this section, we present a more in-depth look at the electronic payment use case mentioned in Section 3 and how it relates to SPUR-oriented design. With electronic payments, drivers will have the ability to pay for parking electronically without interacting with a parking meter or a garage attendant. Drivers will no longer have to dig around for spare change and municipalities will no longer have to collect cash from parking meters.

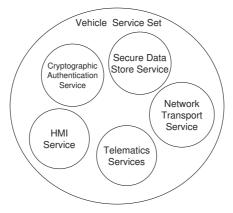

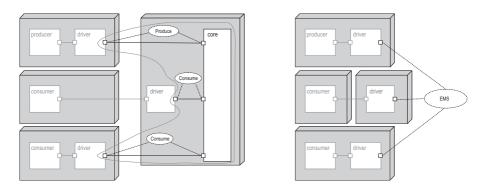

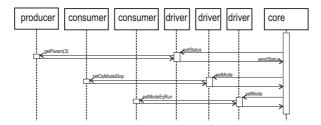

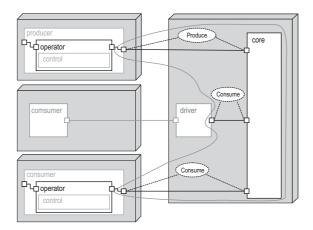

Figure 2 shows a sequence diagram for a vehicle involved in an electronic payment scenario with a parking garage. The main entities in the diagram are the driver of the vehicle, the vehicle's software systems (implemented in a service-oriented architecture, as shown in Figure 3), the vehicle's OEM (or a delegate of the OEM), and the parking garage authority. When the vehicle enters the garage, the garage transmits a list of services and their costs to the vehicle, which in turn presents this information to the driver through the vehicle's HMI.

Fig. 3. The vehicle services needed to implement electronic payment in a serviceoriented architecture

Assuming that the driver is willing to pay the cost to park, she acknowledges the cost of service, parks the vehicle and leaves. The vehicle sends a signed acknowledgement to the garage. Later, the driver returns and begins driving out of the garage. The garage calculates the amount of money owed and securely transmits a bill to the vehicle. The vehicle notifies the driver of how much is owed through the HMI and requests that the driver consent to pay. Confirmation from the driver causes the vehicle to transmit an encrypted, signed payment authorization message to the OEM. The OEM, acting in the role of an e-payment service, securely credits the funds to the parking garage and returns a signed receipt to the vehicle showing proof of payment. Finally, the garage sends a signed receipt to the vehicle showing that it has received its requested payment.

Thus, at the end of the interaction between the driver and the garage, the driver has proof from both the OEM and the garage that she has paid what she

owed. The garage has a signed acknowledgement from the driver stating that she understood the cost to park before she parked her vehicle as well as funds deposited by the OEM to pay for parking. The receipts returned to the driver are necessary to prove that she paid for services in the case of a dispute between the garage and driver. Similarly, the signed acknowledgement agreeing to the cost of parking from the driver is necessary to dissuade a driver from reneging on payment upon exit from the garage.

#### 4.1 Challenges

There are many challenges involving SPUR in the context of such an automotive e-payment system. While many of these challenges are not unique to e-payments in general, the scope of this paper is to understand how these issues are unique in an automotive context.

First are questions of infrastructure. E-payments require a secure, potentially private, system for transferring money from a driver or other occupant in the car to a specific payee. We also assume that these payments will reflect current cash payment characteristics, specifically, we need to support individual transactions of less than one dollar. This requires the support of a third party to aggregate payments on both sides of the payment. This could be the vehicle manufacture, as we've outlined before, a credit card issuer, or an Internet e-payment provider.

Automotive e-payment is inherently a mobile application. Malicious agents are likely to have easy access to all communication that takes place outside the vehicle. In addition, unlike personal mobile devices such as a cell phone, there is inherently less physical security over the vehicle. Cars are often parked in public spaces, and routinely in control of mechanics. Even users sometime have a vested interest in modifying the vehicle software, as evidenced by powertrain modification chips. These reasons imply that some type of end-to-end assurance is needed about the legitimacy of each individual transaction. However, there is an inherent trade-off between the sophistication of a given security system and the risk of compromise. For example, an individual driver is unlikely to notice or care if a individual penny or quarter is missing from his car when she takes it in for service. Similarly, users often trade off convenience for increased risk of monetary loss. For example, many electronic cash cards such as the Octopus card used in Hong Kong [10] require no authentication to use, and the owner assumes that a lost card implies the money associated with that card is also lost. Similarly, in-vehicle e-payment systems need to take into account the unique environment when trading off risk with cost. Mobility also has implications for the reliability of the system. There is no guarantee that a device will always stay in communications range during the period of a transaction.

Providing security and privacy in electronic transactions naturally implies the use of cryptographic protocols. In contrast to general purpose computers, the computational power and upgrade capabilities of embedded devices is severely limited. In addition, unlike the consumer electronics side of the embedded, mobile marketplace, vehicle software has a useful life of over ten years. In this context, how do we ensure that the computational power will be great enough

to support key lengths that can't be easily compromised long into the future, without needless expense? At the same time, flaws in cryptographic protocols are not uncommon, so the in-vehicle software should be upgradable, without causing undue burden on the driver.

Second, are questions of authentication. How do we authenticate that the person responsible for the account used in the transaction is authorized to make the payment? We can't always assume that the driver is authorized to make payments with an account associated with the vehicle. Valets or even teenage drivers quickly complicate this assumption. At the same time, we want to authenticate the payee to the driver, making sure that a hacker hasn't set up their own virtual toll booth at the side of the highway, while still making it easy for small businesses to use the system. In some sense, the physical nature of our scenario provides opportunities not usually seen on the Internet. Most drivers require a physical or electronic key in order to enter a vehicle. At the same time, in the scenarios that we described, the payee will be in physical view of the driver. This presents an opportunity to provide out-of-band signaling to facilitate authentication.

Similarly, the physical nature of owning a vehicle presents an opportunity for associating real people with digital identities. In buying or leasing a vehicle, most buyers have little expectation of privacy. Most transactions require some type of financing, necessitating at least a credit check. Even in situations where this isn't the case (e.g. person to person cash transactions), owning a vehicle requires licensing with the state, another transaction which implies a lack of privacy, and a financial interest in correctly identifying the owner.

Finally, the interface between the driver and the vehicle computer system poses several important challenges. Because we are talking about the driver authorizing payments while driving, this interaction needs to require little attention from the driver. At the same time, we need drivers to understand the security implications of the actions they're performing. Studies of web browser security have demonstrated techniques to better inform users of the security implications of the current browser state [11].

## 5 Modeling Requirements

The electronic payment use case detailed in Section 4 touches on all aspects of SPUR-oriented design. For vehicular electronic payment to be widely accepted, sensitive financial information must be securely exchanged between the vehicle, the OEM, and a service vendor. The privacy of financial dealings must also be preserved. Furthermore, the HMI must clearly present information about the cost of a service and indicate when consent is required. Finally, electronic payment systems must be reliable enough to give drivers the confidence to wholly adopt them.

In order to design an electronic payment system, it's important to model various aspects of the design before building a production system. This modeling would allow designers to understand how the intended system meets these and

other important attributes. However, modeling the parking garage use case requires a diverse set of tools and disciplines. The driver must not be distracted while making financial transactions yet the HMI must be involving enough to assure the driver that they are making a secure transaction. The HMI may use a text display, an LCD, voice recognition, or a combination of interface technologies to communicate with the driver. We must be able to realistically model a user interface with all of these qualities.

A significant amount of software of varying complexity is involved in our use case, from less complex programs embedded in the vehicle to highly complex back-end software at the OEM and parking garage vendor. The interactions between the vehicle, the OEM, and the service vendor must be modeled as well. We thus require a software modeling tool that can effectively model heterogeneous software environments with varying levels of complexity.

Each aspect of SPUR is a whole-system attribute. For example, spending resources on creating a security-hardened implementation of the vehicle's embedded programs is useless if the communications between the vehicle and OEM are unencrypted. Similarly, an electronic payment system with a highly reliable embedded program but a buggy OEM back-end interface makes the system as a whole unreliable.

Therefore, to fully evaluate each aspect of SPUR we must be able to study the HMI of the vehicle, its embedded programs, the OEM and parking garage enterprise software as a single system. We require a single tool or suite of tools that can fully inter-operate in order to model the interactions between each of the system's components. The tool must allow us to inject faults or directed attacks and measure the effects both in terms of software metrics (i.e. loss of privacy, reduced reliability) and in terms of customer-facing metrics such as the effect of a fault at the OEM on the in-vehicle HMI.

While many existing tools could be used to realize this goal, there are some important requirements that should be met. First, it's important for a model to accurately reflect the design of the final product. A software system that is modeled in one tool and then completely redesigned and rewritten for production is likely to provide little value in predicting security and reliability concerns. At the same time, a modeling tool needs to allow abstractions that simplify the process of quickly building a model that can be tested before the design is finalized. Another important requirement is a tool that can easily inter-operate with other tools. While a single tool that can model everything from the HMI to the back end database might be simpler, it is unlikely to ever meet all the needs of designers and researchers. Instead such a system is likely to be tested using a suite of tools tied together to meet the unique needs of the team.

Overall, the important attributes for a system for modeling SPUR attributes has less to do with the individual tool features, but more to do with the ability of the tool to adapt to the goals of the modeling project. For example, techniques for compromising the security of a system are constantly evolving. A single tool is unlikely to meet the needs of a system security audit without adapting to new techniques. At the same time, the local resources and techniques available to

a design team are likely to be unique. However, we believe that a system level approach to modeling new systems provides a valuable approach to understanding how the SPUR attributes are preserved by a given design.

#### 6 Related Work

While we could not hope to completely cover all relevant works in the individual disciplines of security, privacy, usability and reliability, in this section we present key related work in each of the SPUR attributes related to information systems in the automotive domain.

- Security As vehicles become connected to exterior networks, such as through telematics systems, the possibility of malicious hacking of vehicle networks increases. Wolf et al. [12] investigate the vulnerabilities of several common vehicle networking technologies including CAN, FlexRay, and LIN.

- Privacy Privacy is a concern in any system where vehicles broadcast their GPS location on a regular basis. A powerful entity, such as a government, could attempt to track the locations of individual vehicles if countermeasures are not taken. Sampigethaya et al. [13] have devised CARAVAN as a way to ensure location privacy in these types of systems. CARAVAN works by, among other techniques, grouping clusters of vehicles together and periodically nominating a new group leader to broadcast probe data while other vehicles remain silent.

- Usability Usability is probably the most familiar attribute to the general public. Most people have experienced the frustration of trying to turn on the windshield wipers, for example, in an unfamiliar car. A lot of research has been performed in understanding driver distraction as it relates to the usability of various in-car features. For example, Nowakowski et al. investigate usability problems with in-vehicle navigation systems [14].

- Reliability Reliability is also extremely important to the automotive industry and the embedded systems community in general. Unlike a desktop computer, an embedded system, such as an automotive powertrain controller, is expected to work all the time or at least fail in a way that doesn't leave the driver stranded on the side of the road. Tindell et al. look at formal methods for designing safe automotive software [15].

### 7 Conclusion

Given the transformation that both the nature and terrain of computing in the automobile are undergoing, this paper has outlined the case to model security, privacy, usability and reliability (SPUR) in the context of the software enabled services associated with the automobile. SPUR represents a set of attributes that are not explicitly articulated or demanded by the end customer or consumer and hence, broadly speaking, SPUR represents non-functional, or para-functional, attributes.

Security, privacy, usability and reliability have all been product creation requirements that have been well understood and refined by the automotive industry over the years, but almost exclusively in the mechanical or physical context. With the advent of the information-enabled automobile — connected to the road-side infrastructure and to consumer devices — SPUR takes on a very different interpretation. This paper highlights the importance of SPUR. In addition, we make a case for modeling SPUR, as this would avoid costly and time consuming hardware investments and will likely provide quick insights into how technologies and standards could be adapted to meet automotive SPUR requirements.

#### References

- Patterson, D.A.: 20th century vs. 21st century C&C: The SPUR manifesto. Commun. ACM 48(3), 15–16 (2005)

- Navet, N., Song, Y., Simonot-Lion, F., Wilwert, W.: Trends in automotive communication systems. Proceedings of the IEEE 93(6), 1204–1223 (2005)

- 3. Bradley, D., Seward, D., Dawson, D., Burge, S.: Mechatronics and the Design of Intelligent Machines and Systems. Stanley Thornes Ltd., London (2000)

- 4. Messerschmitt, D.G., Szyperski, C.: Software Ecosystem: Understanding an Indispensable Technology and Industry. MIT Press, Cambridge (2003)

- 5. AUTOSAR GbR: AUTOSAR website (2005), http://www.autosar.org/

- 6. Jameel, A., Stuempfle, M., Jiang, D., Fuchs, A.: Web on wheels: Toward internet-enabled cars. Computer 31(1), 69–76 (1998)

- US Department of Transportation: Vehicle infrastructure integration (2006), http://www.its.dot.gov/vii/

- 8. Nelson, E.C., Prasad, K.V., Rasin, V., Simonds, C.J.: An embedded architectural framework for interaction between automobiles and consumer devices. In: IEEE Real-Time and Embedded Technology and Applications Symposium, pp. 192–199 (2004)

- 9. Papazoglou, M.P., Georgakopoulos, D.: Service oriented computing. Commun. ACM 46(10), 24–28 (2003)

- Paynter, J., Law, P.: An arm's length evaluation of Octopus (2006), http://www.code.auckland.ac.nz/e-comWorkshop/work/An/arms/length/evaluation/of/Octopus.pdf

- 11. Ye, Z(E.), Smith, S., Anthony, D.: Trusted paths for browsers. ACM Trans. Inf. Syst. Secur. 8(2), 153–186 (2005)

- 12. Wolf, M., Weimerskirch, A., Paar, C.: Secure in-vehicle communication. Embedded Security in Cars: Securing Current and Future Automotive IT Applications (2005)

- Sampigethaya, K., Huang, L., Li, M., Poovendran, R., Matsuura, K., Sezaki, K.: CARAVAN: Providing location privacy for VANET. In: Embedded Security in Cars (ESCAR) (2005)

- 14. Nowakowski, C., Green, P., Tsimhoni, O.: Common automotive navigation system usability problems and a standard test protocol to identify them. In: ITS-America 2003 Annual Meeting, Intelligent Transportation Society of America (2003)

- 15. Tindell, K., Kopetz, H., Wolf, F., Ernst, R.: Safe automotive software development. In: DATE 2003: Proceedings of the conference on Design, Automation and Test in Europe, Washington, DC, USA, pp. 616–621. IEEE Computer Society Press, Los Alamitos (2003)

# Addressing Cross-Tool Semantic Ambiguities in Behavior Modeling for Vehicle Motion Control

Sandeep Neema<sup>2</sup>, Sushil Birla<sup>1</sup>, Shige Wang<sup>1</sup>, and Tripti Saxena<sup>2</sup>

<sup>1</sup> General Motors Corporation, Warren, MI 48090 <sup>2</sup> Vanderbilt University, Nashville, TN 37203

Abstract. Emerging model-based development methods in the Automotive Vehicle Motion Control (VMC) domain are using different tools at various stages of the engineering process. Behavioral models created in various forms of finite state machines have to be exchanged across these tools, but semantic unknowns in modeling environments and semantic variations across tools preclude automated correct interpretation. This research presents an approach to address this issue through an unambiguous, math-based, tool-neutral extended finite state machine metamodel (eFSM) for behavior specifications in the automotive VMC domain. The semantics of the metamodel are anchored to formal specifications in a mathematical framework. Our approach requires modeling with commercial tool environments conforming to the eFSM. The conformance is enforced by exporting the tool native models into eFSM-conformant models and checking them against the well-formed rules encoded as OCL constraints in the eFSM. We have performed "proof of concept" exercises with two commercial tools in transforming their native models into eFSM-conformant forms, and have been able to show that certain ambiguities in both tools can be prevented through the eFSM, promising higher confidence software engineering for the VMC domain.

### 1 Introduction

High integrity functions in Automotive Vehicle Motion Control (VMC) software are becoming increasingly complex as more functions are being realized in software. Factors contributing to the rising complexity include increasing number of interactions, distribution across many electronic control units (ECU-s) and buses, number of different suppliers, and number of engineering stages spread across different disciplines and different tool environments. To add to the complexity, VMC functions are tightly constrained in timing interrelationships, combining discrete and continuous control in ways that are difficult to analyze. The size and complexity of VMC systems have grown beyond the ability to assure their correctness through exhaustive testing and simulation. These difficulties motivate the need for VMC systems engineering processes that prevent errors from the earliest stage and provide work products that are correct by construction [1].

In order to improve engineering quality, industry has been shifting effort from program code level activity towards model based control and software engineering [2,3]. However, it is not possible to transfer model data unambiguously from the tool of one engineering stage to that of another. In other words, different tools are not able to interpret the model with the same meaning. Although tools popular in the VMC engineering process, such as MathWorks Stateflow, I-Logix Rhapsody, and ETAS ASCET, support modeling in the finite state machine (FSM) paradigm, there are semantic unknowns and variations in their FSM-s. Therefore, model data has to be manually interpreted, manipulated and transferred from one engineering stage to the next, imposing penalties in integrity, quality, cost, and time.

Many research and industrial endeavors have addressed cross-tool model exchange issues. Industrial efforts include various standardization activities. ISO 10303 AP 233 [4] extends STEP, the international standard for exchange of product data, to support exchange of behavioral models of various kinds, including the FSM. The Object Management Group (OMG) SysML [5] is developing a standardized system modeling language, as a profile of UML 2.0 [6]. However, UML 2.0 does not have a strong mathematical foundation, e.g., it does not specify constraints on relationships such as generalization-specialization. Thus UML 2.0 does not support unambiguous model transformation and exchange. SAE Analysis Architecture Description Language (AADL) [7] is a modeling language to model system architecture for analysis. AADL focuses on structure and parafunctional properties, and is not suitable for systems engineering activities such as requirement specifications. EAST-ADL [8] was developed as a modeling language for electronic architecture with similar objectives, but does not provide unambiguous semantic support for behavior specification. EAST-ADL relied on external tools and languages for behavioral specifications. In parallel, researchers have endeavored to formally specify the semantics of commercial tools. For example, the formal operational semantics for Stateflow by Hamon and Rushby [9] and the operation semantics of Stateflow in BSpec notation by Kestrel Technologies [10] are two of a dozen published Stateflow semantics. However, the formal semantics defined by these research activities are "reverse engineered", without support from the tool vendors, based on the behaviors observed over a set of examples. Conformance to vendor-implemented semantics is demonstrated in most cases by comparing traces with a few tests. It does not provide adequate confidence for the VMC domain.

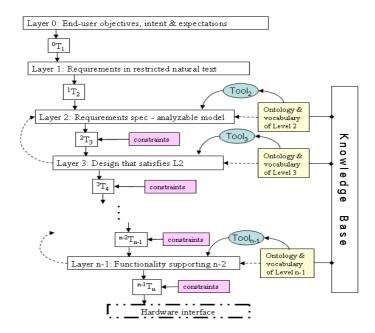

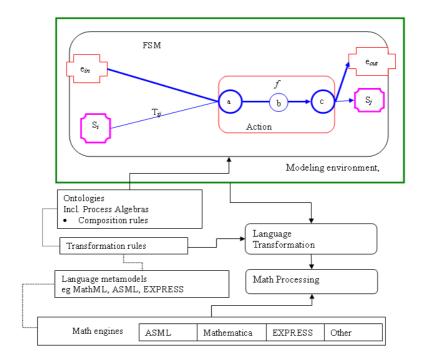

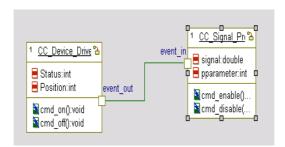

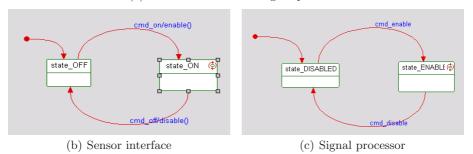

While the international standards and commercial tools seek breadth of application to enlarge their market, we seek disambiguation of model data for a narrowly defined domain of applications, VMC, where integrity is paramount. The scope is limited to statically configured systems with statically defined deterministic behaviors. The typical behavior of a VMC application can be described in a finite state machine with the continuous closed loop control functions embedded in its action elements. The scope of data exchanges includes VMC systems engineering processes such as requirement specification, functional design, analysis of various types, specification of the distributed platform, allocation of

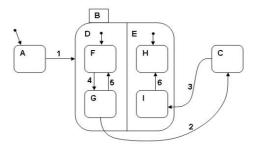

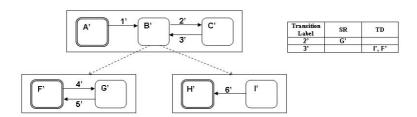

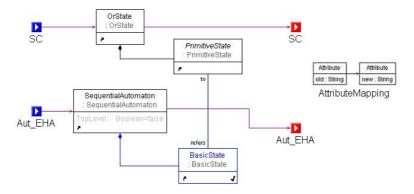

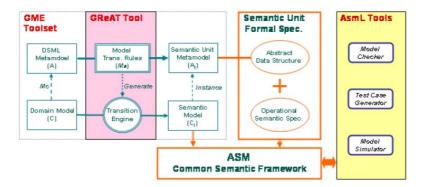

application functions and interactions to platform elements, code generation, integration, verification at every step, and overall validation. Behaviors of this kind can be metamodeled as an extended finite state machine (eFSM). In this paper, we propose an eFSM, with unambiguous semantics anchored in a mathematical foundation, as a well-suited medium for interchange across different stages of the engineering process mentioned above. The proposed approach requires modeling constraints, which are VMC domain-specific to enable a correct-by-construction process.